Inside the Architecture of a Modern Quantum Computing System

An engineering-level reality check from the system stack down

Quantum computing is often portrayed as a story about exotic physics and fragile qubits. In practice, a modern quantum computing system is a deeply layered, hybrid engineering stack where classical hardware, software orchestration, and environmental control dominate as much as — if not more than — the quantum processor itself.

Having worked hands-on with cloud-accessible superconducting systems, quantum annealers, and high-fidelity simulators, my perspective has shifted from “how many qubits do we have?” to a more practical question:

How well does the entire system function as a coordinated, controllable, and scalable machine?

This article walks through the real architecture of a modern quantum computing system — layer by layer — with a focus on what matters in practice, where the bottlenecks truly are, and why system design, not just qubit physics, determines usable performance.

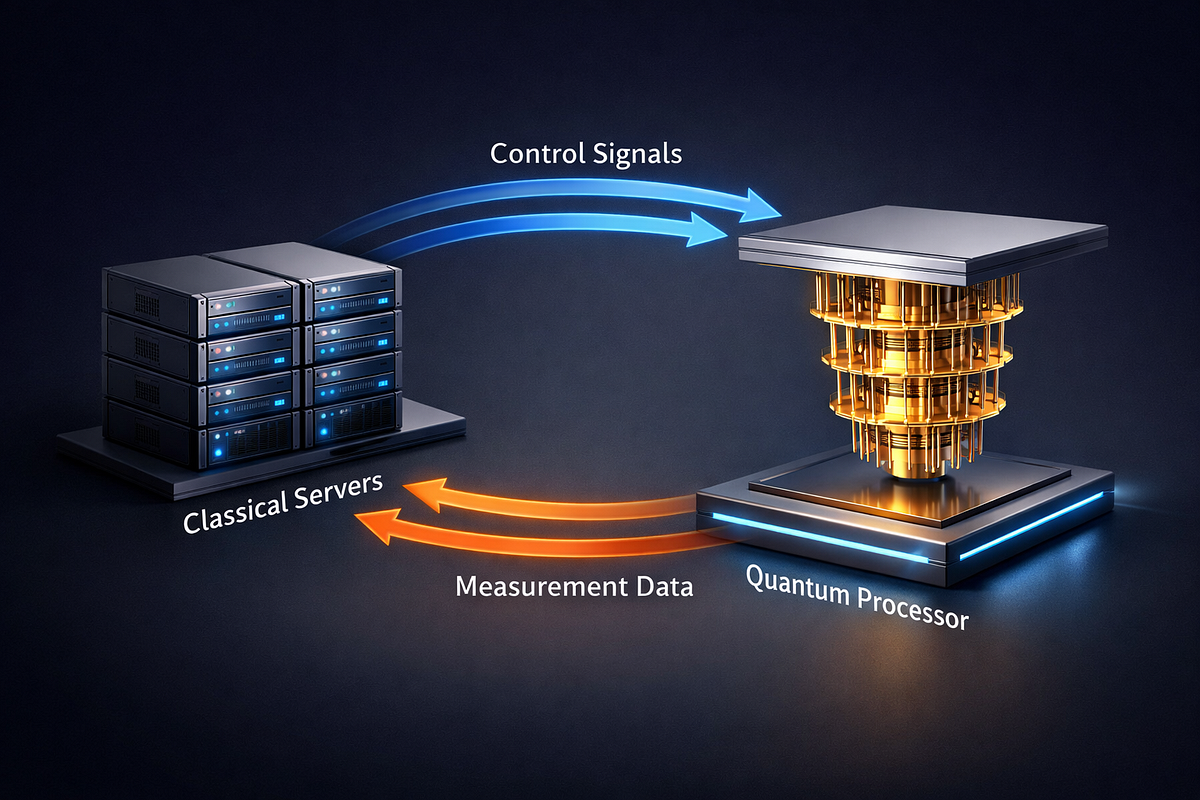

1. The Quantum Computer Is a Hybrid System

The most common misconception I encounter is treating the quantum processor (QPU) as a computer. In reality, the QPU is just one component in a stack dominated by classical infrastructure.

A production-grade quantum computing system typically includes:

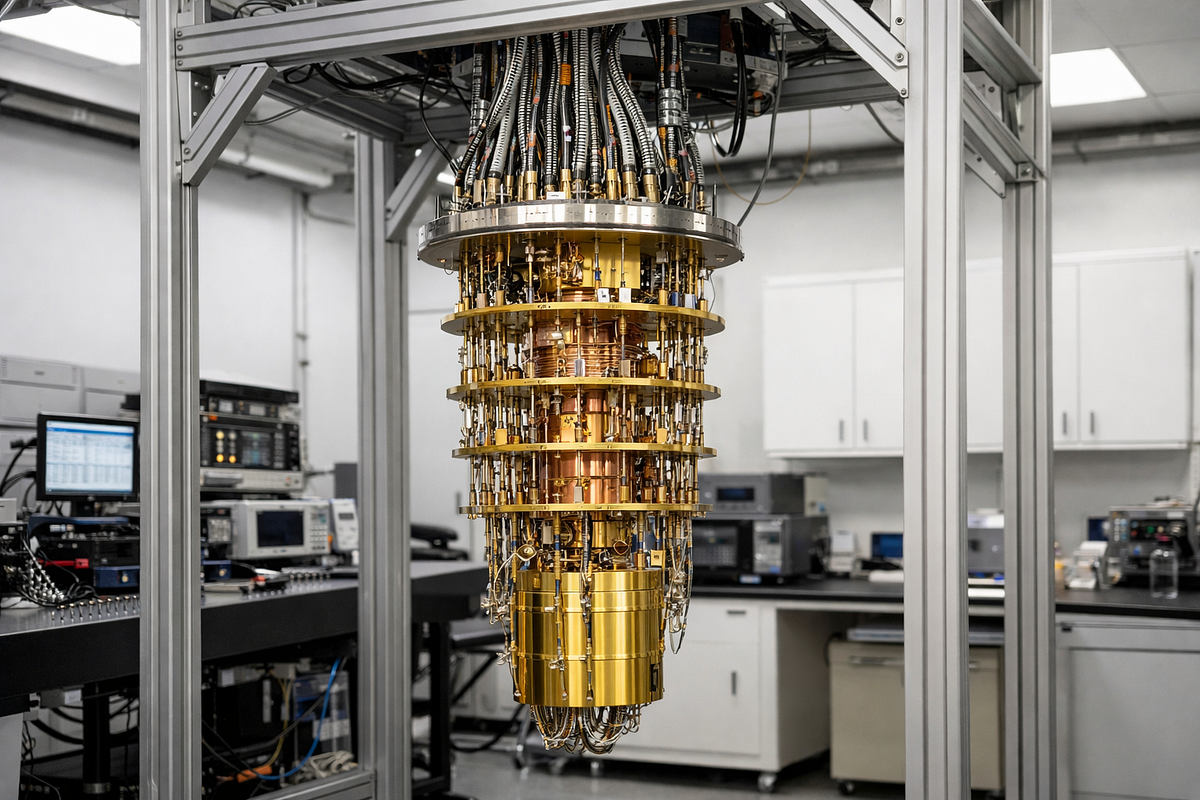

- A quantum processing unit (QPU) containing physical qubits

- Cryogenic and environmental systems that maintain extreme operating conditions

- Control electronics generating and measuring qubit signals

- A classical control and orchestration layer handling timing, scheduling, and feedback

- A software stack including compilers, transpilers, and runtime systems

- Cloud and HPC integration enabling hybrid quantum-classical workflows

From my experience running real workloads, the performance ceiling is almost always set by the classical side of this stack, not just by qubit coherence times.

2. The Qubit Layer: Quality, Not Just Quantity

Qubit counts make headlines, but in practice, effective qubit quality determines what you can actually compute.

What outsiders often miss

Connectivity dominates algorithm design.

On superconducting devices I’ve worked with (5–27 qubits), limited connectivity forced additional SWAP gates, increasing circuit depth and compounding errors. A smaller, well-connected device frequently outperformed a larger, sparsely connected one.

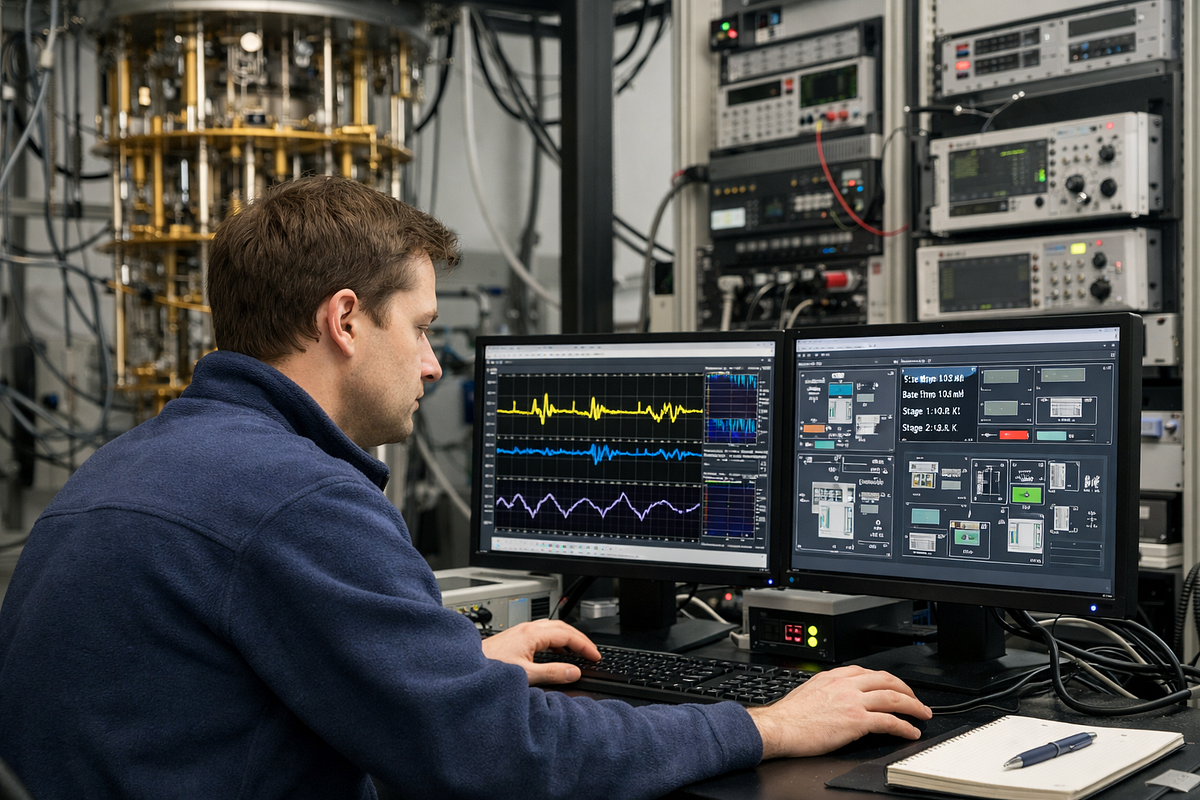

Calibration drift is constant.

Simulators assume stable noise models. Real hardware does not. Gate fidelities and readout errors drift over time, and I’ve seen circuits fail on hardware that worked perfectly in simulation just hours earlier.

Two-qubit gates are the real constraint.

While single-qubit fidelities may exceed 99.9%, two-qubit gates often sit closer to 95–99%. For multi-layer circuits, that difference defines the boundary between usable and meaningless results.

The result is a simple but non-intuitive truth:

A 15-qubit device with stable calibration and good connectivity can be more useful than a 50-qubit device with higher noise and routing overhead.

3. Control Electronics: The Most Misunderstood Layer

If there is one part of the architecture that deserves more attention, it is the classical control stack.

Every qubit operation is driven by precisely shaped microwave or laser pulses generated by room-temperature or cryogenic electronics. These systems define:

- Gate timing precision

- Crosstalk between qubits

- Readout accuracy

- Synchronization across the processor

In multiple experiments, I’ve observed cases where improving scheduling and pulse timing produced larger fidelity gains than changing the quantum circuit itself.

The scaling problem

Each added qubit increases demands on:

- DAC/ADC channels

- Microwave generation hardware

- FPGA or ASIC-based controllers

- Signal routing into the cryostat

This does not scale linearly. Wiring complexity, signal integrity, and thermal load quickly become architectural bottlenecks.

Room temperature vs cryogenic control

Most current systems rely heavily on room-temperature electronics, which are easier to engineer but introduce latency and wiring challenges. Moving more control closer to the qubits (cryo-CMOS, cryogenic amplifiers) reduces latency but introduces severe power and thermal constraints.

From a system perspective, scaling control electronics cleanly is at least as hard as scaling qubit fabrication.

4. Cryogenics and Environmental Systems: The Invisible Constraints

Superconducting quantum processors operate at temperatures near 10–20 millikelvin. Maintaining that environment is a full engineering discipline.

Practical constraints I’ve seen impact experiments

- Cooling capacity limits qubit growth. Every control line adds heat load. More qubits mean more wiring, which stresses the refrigeration system.

- Vibration and EMI matter. Mechanical noise or electromagnetic interference can measurably degrade coherence. These effects never appear in algorithm papers but frequently show up in real systems.

- Thermal management shapes architecture. Decisions about multiplexing, amplifier placement, and control line design are often driven by thermal budgets, not theoretical optimality.

Cryogenics are not just a supporting system; they define the operational envelope of the entire QPU.

5. The Software Stack: Where Abstractions Break

Quantum programming frameworks give the impression that hardware details are abstracted away. In reality, the abstraction leaks constantly.

Where theory meets hardware constraints

Circuit mapping is never neutral.

High-level algorithms assume ideal connectivity. On real devices, transpilers insert SWAPs to satisfy topology constraints. I’ve seen routing overhead double circuit depth, pushing experiments beyond coherence limits.

Timing is physical, not abstract.

Gate scheduling must respect pulse-level constraints, measurement windows, and hardware-specific delays. Ignoring this leads to failures that look like “algorithm errors” but are actually control mismatches.

Noise is dynamic.

Noise models used in simulators are static approximations. Real devices drift, meaning mitigation strategies must continuously adapt.

The lesson: compilers are not just convenience tools; they are performance-critical system components.

6. The Classical–Quantum Interface: The Real Bottleneck

Modern quantum workloads are rarely standalone quantum circuits. They are hybrid loops involving iterative feedback between classical and quantum processors.

This interface introduces three major constraints:

Latency

Variational algorithms and error mitigation often require rapid classical feedback. Delays in measurement processing or cloud orchestration directly reduce usable circuit depth.

Bandwidth

Each qubit requires multiple control and readout channels. Scaling to hundreds of qubits multiplies signal demands, leading to congestion and crosstalk.

Orchestration complexity

Scheduling thousands of time-sensitive operations under noise and hardware constraints is an HPC-style coordination problem. From my experience, orchestration inefficiencies often waste more potential performance than raw hardware noise.

7. Error Mitigation vs. Error Correction: Two Very Different Challenges

These terms are often conflated, but architecturally, they represent different worlds.

Error mitigation (today)

Mitigation techniques helped me extract usable signals from noisy hardware, but they come with costs:

- Require precise, frequently updated noise models

- Increase runtime through repeated sampling

- Break down for deeper circuits

They are a software-hardware co-design problem, not a magic fix.

Error correction (future)

True fault tolerance will require:

- Hundreds to thousands of physical qubits per logical qubit

- Real-time classical processing for syndrome decoding

- Ultra-low-latency feedback paths

This is a system integration challenge on a scale far beyond current devices.

8. What Benchmarking Taught Me About “Performance”

When comparing systems, the most useful metrics were not the ones in marketing materials.

What mattered in practice:

- Effective circuit fidelity, not individual gate specs

- Connectivity and routing overhead

- Calibration stability over time

- Classical orchestration latency

- System availability and queue times

I have seen smaller, stable systems deliver more usable results than higher-qubit machines with poor calibration consistency.

9. Industry Hype vs. Engineering Reality

Several recurring narratives do not match system-level reality:

The most important advances I see today are not in qubit counts but in control engineering, compiler sophistication, and hybrid orchestration.

10. From Lab Prototype to Deployable System

Turning a lab setup into a usable quantum computer requires:

- Stable, repeatable calibration

- Scalable control wiring and electronics

- Automated software orchestration

- Environmental robustness

- Secure, cloud-accessible interfaces

In advisory work with organizations exploring quantum adoption, the biggest gap was not algorithm knowledge — it was understanding how far current systems are from plug-and-play infrastructure.

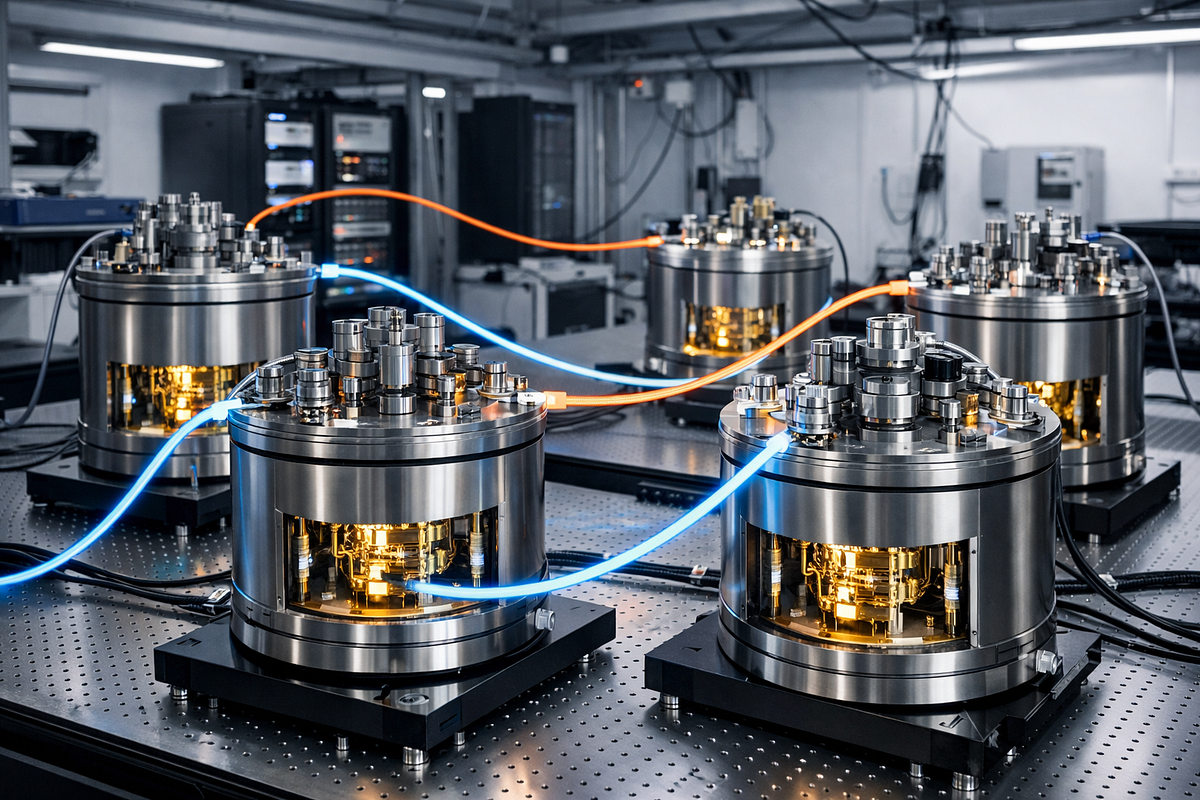

11. The Architectural Future: Modular and Distributed

Over the next decade, the most important shifts will likely include:

- Modular QPU architectures connected via photonic or microwave links

- Cryogenic control electronics to reduce latency and wiring

- Distributed quantum systems coordinated by classical HPC infrastructure

- Deeper hardware–software co-design at the compiler and orchestration level

Scaling will come from architectural innovation, not just denser qubit chips.

12. Skills the Next Generation of Engineers Will Need

Future quantum system engineers will require:

- Classical electronics and signal integrity expertise

- FPGA/ASIC and control firmware skills

- Quantum software and compiler knowledge

- Experience with calibration, noise characterization, and system monitoring

- Strong systems architecture thinking

Quantum computing is not just a physics problem; it is one of the most interdisciplinary engineering challenges in modern computing.

Conclusion: Architecture Defines Capability

After years of working across quantum software, system benchmarking, and hybrid workflows, one conclusion stands out:

A quantum computer is only as powerful as its full system architecture allows it to be.

Qubits matter — but so do control electronics, cryogenics, compilers, orchestration layers, and classical integration. Progress in quantum computing will be determined not just by breakthroughs in qubit physics, but by how effectively we engineer these layers into scalable, reliable systems.

Understanding that architecture is the difference between believing the hype and building real, usable quantum machines.

Comments

Post a Comment